# How the history began

Two friends with a passion for electronics in a garage of Arezzo

EMBEDDED CREATORS SINCE 1979

### SECO at a glance

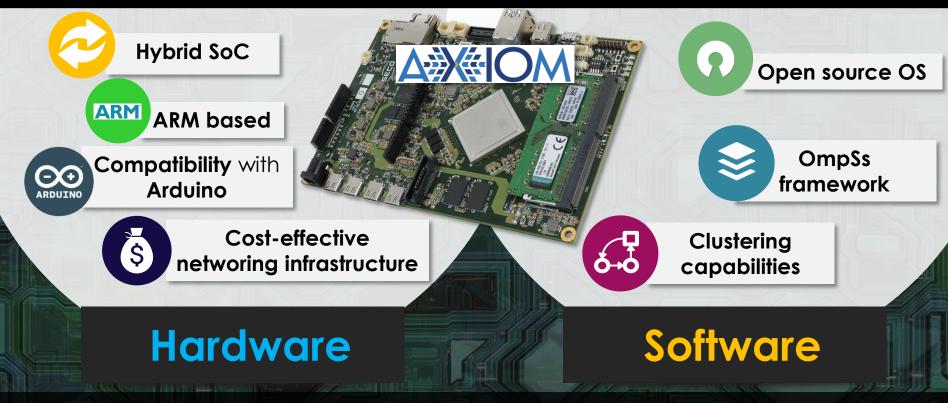

### **AXIOM Ecosystem**

H2020 allowed SECO to invest in the Programmable hybrid ARM/FPGA SoCs area bringing new solutions to the embedded market through relationships with both industrial and academic partners

#### **INDUSTRIAL PARTNERS**

#### **ACADEMIC PARTNERS**

### Background Scenario: The Market Needs

# CYBER-PHYSICAL AGE

Things have to become as smart as people in order to improve and simplify human behavior

### Our proposal: AXIOM

Hardware and Software Stack Solution

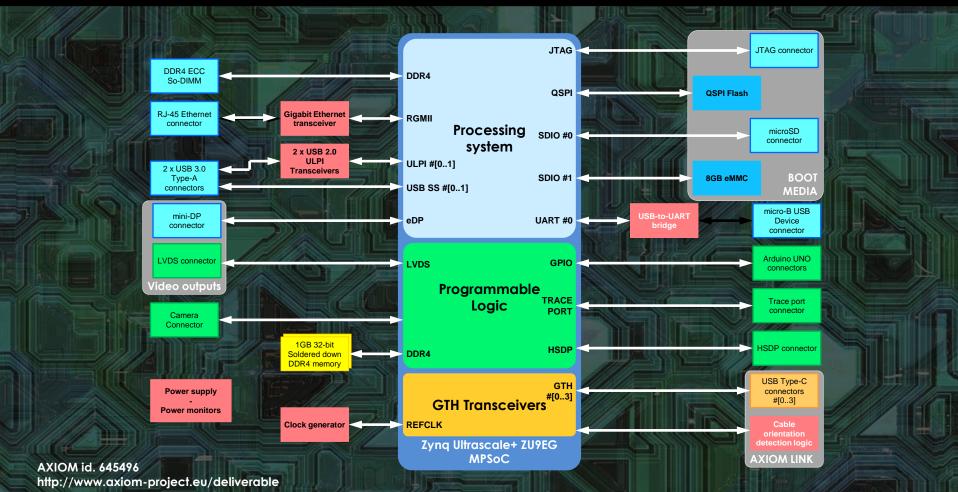

### AXIOM hardware prototype

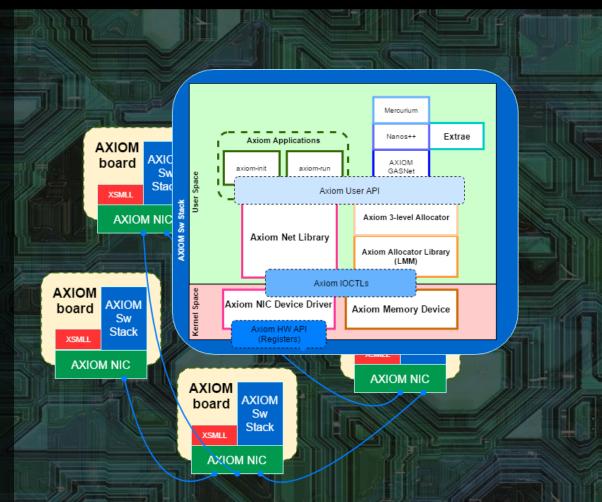

### Cluster Software Architecture

- Linux BSP supporting on-board hardware

- Libraries to provide applications a convenient interface to hardware

- User level applications for system configuration

- Remarkable examples:

AXIOM link, power monitors,

memory allocation

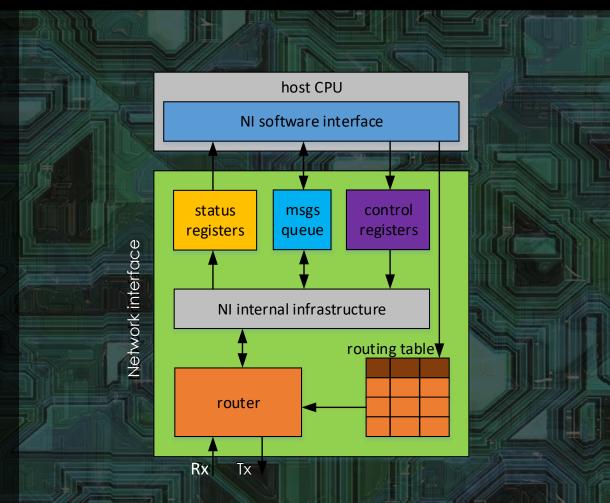

### AXIOM LINK – NIC e SW I/F

- Support for different topologies: ring, 2D mesh, irregular

- Automatic link status monitoring and interconnect discovery

- Supports the transmission of 2 different message types

- RDMA transfers

AXIOM id. 645496 http://www.axiom-project.eu/deliverable

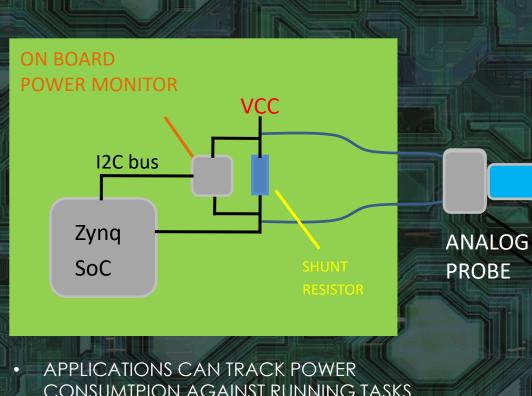

## Power Monitoring and Profiling

#### **Dedicated On-Board Hardware:**

Power measurements on 8 supply rails (70% of maximum total estimated power)

Specific Development Tools **Cross Triggering Capabilities During Debug and Trace:**

Dedicated test points for analog probe connections and 'Breakpoint' on given power consumption levels

**AXIOM id. 645496** http://www.axiom-project.eu/deliverable

- CONSUMTPION AGAINST RUNNING TASKS

- USERS MAY TEST CODING STYLES AGAINST POWER CONSUMPTION

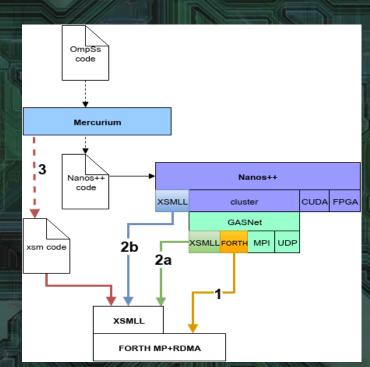

### PROGRAMMING MODEL – OmpSs support

Exploit **parallel computation** of a sequentially written application over the AXIOM cluster.

- OmpSs@cluster

- OmpSs@FPGA

Specific extension of OmpSs components have been developed

AXIOM Specific component was required at the networking layer (GASNet), a dedicated conduit has been developed

### Programming Model – OmpSs support

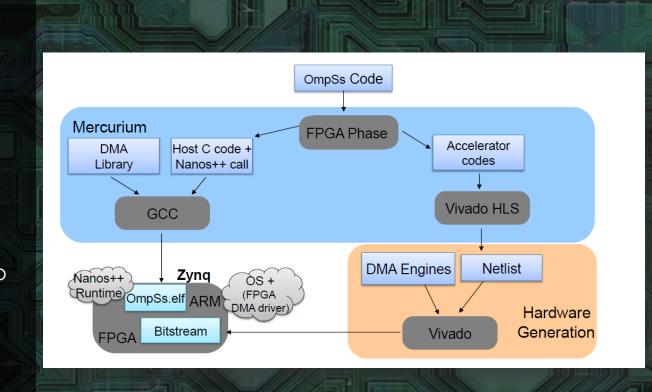

#### OmpSs@FPGA

- New target in mercurium, in order to drive bitstream build with Vivado HLS compiler

- Runtime systems was adapted to spawn tasks to the FPGA and support data trasfers using a specifically developed DMA library

## Proof of concept scenarios

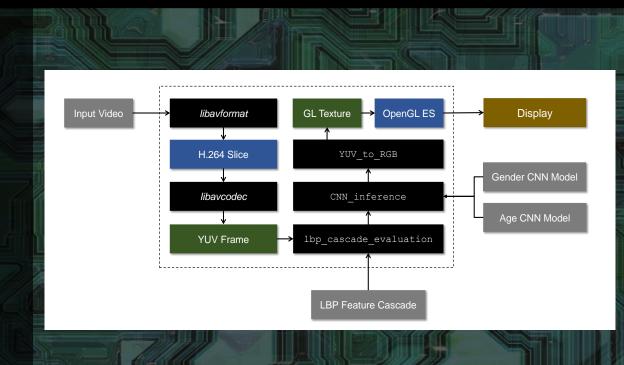

**SVS - face detection** for gender identification and age estimation

- Security

- Customer profiling for the retail sector

AXIOM id. 645496 http://www.axiom-project.eu/deliverable

### Proof of concept scenarios

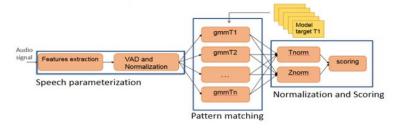

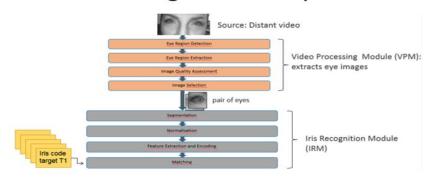

Smart Home Living scenario - identification system which combines the analysis of two different biometrics:

- Iris recognition

- Speaker identification

The purpose of this scenario is to enforce the security of access while improving the interaction of the user with the smart home in a natural way.

#### Speaker identification subsystem

#### Iris Recognition subsystem

### Value proposition

**Power efficient**

Reconfigurable

**FLEXIBILITY**

Scalability

Shrink HPC Clusters to the Embedded World

Easy parallel programming

MODULARITY

Agile, eXtensible, fast / O Module for the cyber-physical era

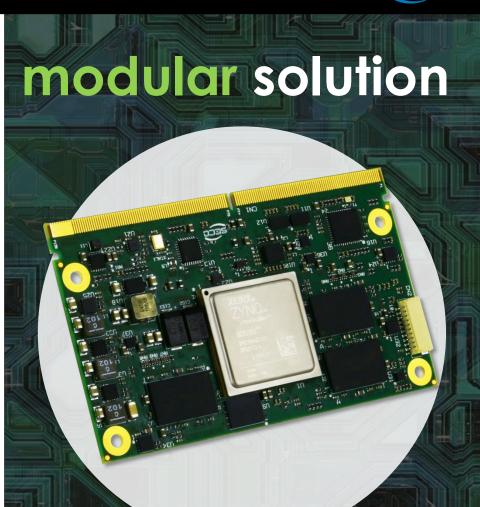

### SM-B71: SECO industrial solution

- Wide scalability from Dual-Core to Quad-Core ARM ® Cortex ®-A53 MPSoCs with GPU/VCU

- Dedicated Real-Time ARM® Cortex®-R5processors

- Extreme flexibility: up to 256k FPGA logic cells

- LVDS and DP video interfaces up to 4K resolution Highspeed interfaces

- Dual memory interface (CPU/FPGA)

- MultiGb transceivers

# Out of the Lab

**SMART HOME**

DO- IT-YOURSELF

**SMART CAR**

**SMART ENERGY**